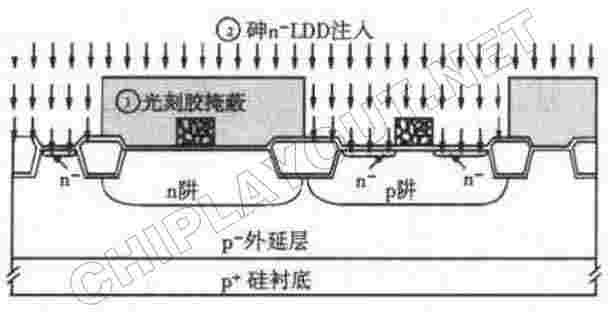

随着栅的宽度不断减小,栅结构下的沟道长度也不断的减小, 为了有效的防止短沟道效应,在集成电路制造工艺中引入了轻掺杂漏工艺(LDD),当然这一步的作用不止于此,大质量材料和表面非晶态的结合形成的浅结有助于减少源漏间的沟道漏电流效应。同时LDD也是集成电路制造基本步骤的第四步。

- N-轻掺杂漏注入(nLDD)

- N-LDD光刻

刻印硅片,得到N-区注入的光刻胶图形,其它所有的区域被光刻胶保护 - N-LDD注入,在未被光刻胶保护的区域进入砷离子注入,形成低能量浅结(砷的分子量大有利于硅表面非晶化,在注入中能够得到更均匀的掺杂深度)

- N-LDD光刻

- P-轻掺杂漏注入(pLDD)

- P-LDD光刻

刻印硅片,得到P-区注入的光刻胶图形,其它所有的区域被光刻胶保护 - P-LDD注入

采用更易于硅表面非晶化的氟化硼进入注入,形成的也是低能量的浅结

- P-LDD光刻

- CMOS制作基本步骤的相关文章

- CMOS制作步骤(一):双阱工艺(twin well process)

- CMOS制作步骤(二):浅槽隔离工艺STI(shadow trench isolation process)

- CMOS制作步骤(三):多晶硅栅结构工艺(poly gate structural process)

- CMOS制作步骤(四):轻掺杂漏注入工艺LDD(lightly doped drain implants process)

- CMOS制作步骤(五):侧墙的形成(side wall spacer formation)

- CMOS制作步骤(六):源/漏注入工艺(S/D implant process)

- CMOS制作步骤(七):接触(孔)形成工艺(contact formation)

- CMOS制作步骤(八):局部互连工艺LI(Local Interconnect process)

- CMOS制作步骤(九):Via-1, Plug-1及Metal-1互连的形成(Via-1 and Plug-1 formation)

- CMOS制作步骤(十):Via-2, Plug-2,Metal-2及Top Metal形成(Via-2,Plug-2,metal2 interconnect and top metal formation)